These methods of communication share all the same issues and have much worse latency and lower bandwidth. Furthermore, connecting multiple servers typically means using Ethernet or InfiniBand.

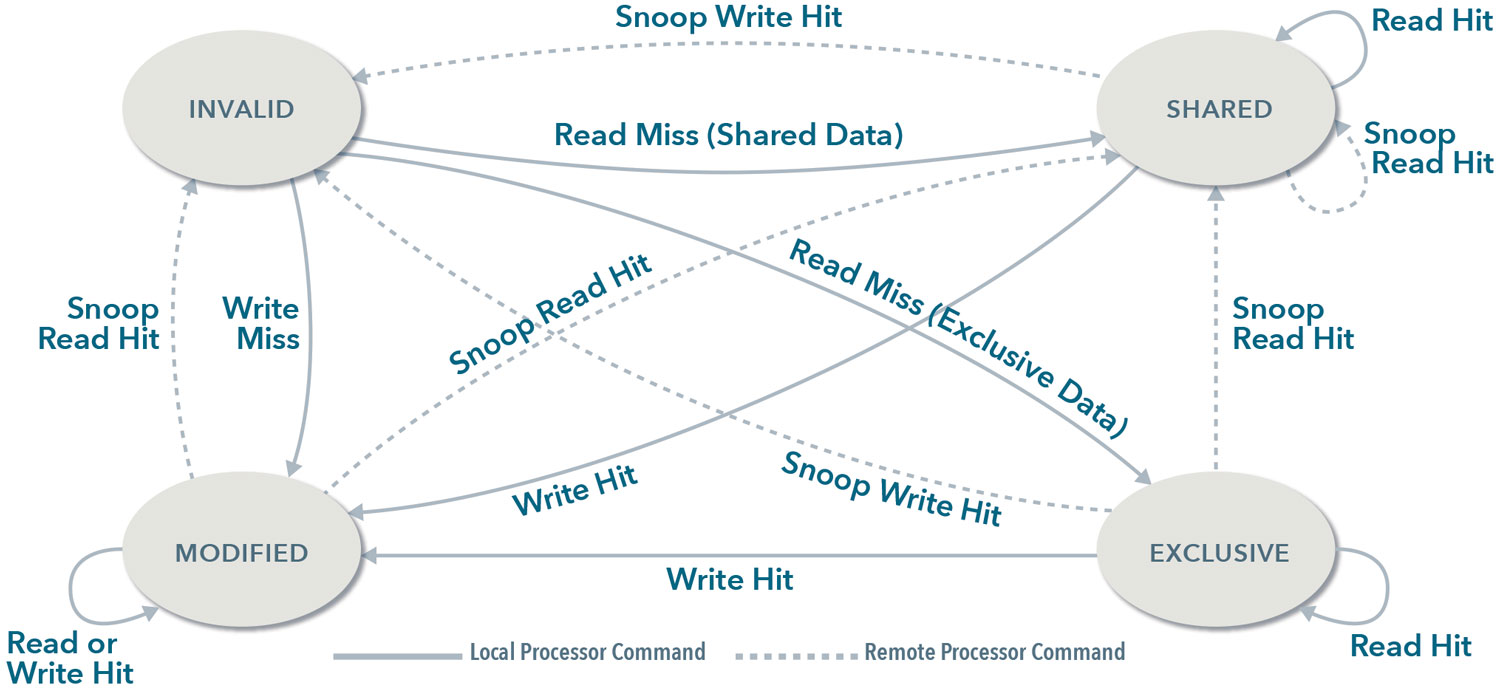

#CXL CACHE COHERENCE SOFTWARE#

With PCI Express, the overhead for communicating between different devices was relatively high from a performance and software perspective. Coherency helps manage and equalize this. Letters are coming in asynchronously, often days after new information has made the letter containing the original information obsolete. A non-technical analogy for these two concepts is if you think about servers like a post office.

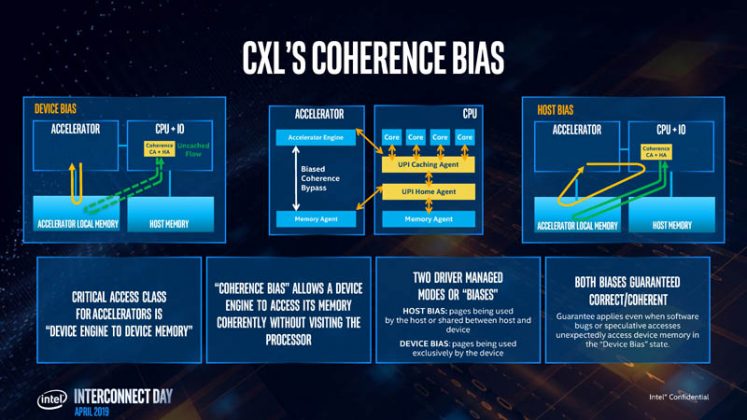

The biggest drawback is that this standard lacked cache coherency and memory coherence. The datacenter is the new unit of computing.Ĭonnecting chips within a server has typically been done with PCI Express. The change in how systems are built moves the unit of compute up from a single chip or server to the entire datacenter. Gordon Moore In The Original Paper Which Predicted “Moore’s Law” – “Cramming more components onto integrated circuits” – 1965 The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically.ĭr. It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. Instead of designing chips for entire workloads, it would be far more cost-effective to design chips for classes of computation and connect them in whatever configuration the specific workload desires. ” In short, the fixed costs of designing chips are soaring due to photomask set costs, verification, and validation. This idea was examined in our article titled “ The Dark Side Of The Semiconductor Design Renaissance. ĭesigning specific chips with the exact computational resources for each workload is prohibitively expensive. Heterogeneous compute reigns supreme as specialized ASICs can provide more than 10x the performance in specific tasks with fewer transistors. One of the ultimate examples of the law of diminishing return is that each incremental transistor spent on general-purpose CPU performance delivers incrementally less performance. These trends all point to a tide of specialization of computational resources. In our advanced packaging series, we dug into the slowdown of Moore law and the impacts of the death of semiconductor cost scaling. The focal point is how cost-effectively one can deliver total compute performance and hook it all together. Over the last decade, the battle has changed with the advent of scale-out and cloud computing. Servers from a decade ago mostly look the same as servers from today. In the past, datacenter chips were primarily about building better CPU cores with faster memory. There are more than 200 members of the CXL Consortium, but these are the companies we believe have the most impactful products and IP. The companies we will be discussing are Intel, AMD, Nvidia, Ayar Labs, HPE, Microsoft, Meta, Google, Alibaba, Ampere Computing, Samsung, SK Hynix, Micron, Rambus, Marvell, Astera Labs, Microchip, Montage Technology, Broadcom, and Xconn. The products from these 20 companies will include CPUs, GPUs, accelerators, switches, NICs, DPUs, IPUs, co-packaged optics, memory expanders, memory poolers, and memory sharers. One of the best semiconductor investors we know once said that accurately understanding and framing the impact of CXL on the datacenter will be the most important source of alpha within semis, and we agree.

#CXL CACHE COHERENCE UPDATE#

In the second half of the report, we will be conducting a status update discussing upcoming products that will utilize CXL from 20 different semiconductor companies, including market opportunity, timing, and capabilities. This article discusses composable server architecture, heterogeneous compute, and versions 1, 2, and 3 of the CXL standard. The 3rd generation of the Compute Express Link (CXL) specification was just announced, and it brings about some significant changes that were missing in prior versions of this standard. Traction for the Compute Express Link (CXL) is reaching a critical mass as every major semiconductor and datacenter company has joined the standard with a wave of 1st generation devices nearing release.

0 kommentar(er)

0 kommentar(er)